# **DSG-NPS R&D** Meeting Minutes

**Date:** August 24, 2021 **Time:** 11:00 AM – 12:15 PM

<u>Attendees</u>: Mary Ann Antonioli, Aaron Brown, Pablo Campero, Brian Eng, George Jacobs, Mindy Leffel, Tyler Lemon, Marc McMullen, and Amrit Yegneswaran

### 1. <u>Hardware Interlock System development</u>

Mary Ann Antonioli, Peter Bonneau, Aaron Brown

- 1. Discussed Temperature Map tab for LabVIEW Hardware Interlock Monitoring program

- Temperature map shows average temperature for each sensor

- Map will be revised to show actual temperature for each sensor

| Crystal Zone Electronics Zone Chiller                                  |      |      |      |      |      |      |      |                 |  |

|------------------------------------------------------------------------|------|------|------|------|------|------|------|-----------------|--|

| Main Front Temperatures Back Temperatures Cooling Circuit Temperatures |      |      |      |      |      |      |      | Temperature Map |  |

|                                                                        |      |      |      |      |      |      |      |                 |  |

| Front Crystal Zone Temperature Map                                     |      |      |      |      |      |      |      |                 |  |

| 35                                                                     | 22.0 | 16.5 | 11.5 | 14.5 | 17.5 | 20.0 | 13.5 | ]               |  |

| *                                                                      | 19.5 | 14.0 | 18.5 | 24.0 | 12.0 | 16.5 | 18.5 |                 |  |

|                                                                        | 18.0 | 14.5 | 14.0 | 17.0 | 21.5 | 15.0 | 17.5 |                 |  |

|                                                                        | 16.5 | 24.0 | 21.5 | 22.0 | 17.0 | 16.5 | 20.5 |                 |  |

|                                                                        | 22.0 | 20.5 | 19.5 | 20.5 | 20.0 | 23.0 | 20.5 |                 |  |

|                                                                        | 14.0 | 21.5 | 20.5 | 22.0 | 15.0 | 24.0 | 17.5 |                 |  |

|                                                                        | 23.0 | 18.0 | 25.0 | 17.5 | 24.0 | 24.0 | 15.0 |                 |  |

|                                                                        | 20.0 | 17.5 | 16.5 | 14.5 | 17.0 | 17.5 | 16.0 |                 |  |

| 0                                                                      |      |      |      |      |      |      | 1044 | 1               |  |

| U                                                                      |      |      |      |      |      |      | 1044 |                 |  |

Screenshot of Temperature Map tab for the LabVIEW Hardware Interlock Monitoring program

# 2. Thermal analysis and Ansys simulation

Aaron Brown

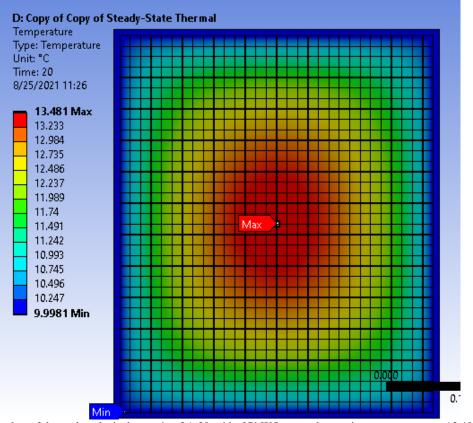

- 1. Reviewed preliminary analysis conducted on full-sized model of 36x30 grid of PbWO<sub>4</sub> crystals surrounded by 1.2 cm Cu shell

- Heat load of 0.5 W applied to rear face of each crystal

- Maximum temperature (located on central crystal) of 13.48°C

- Model needs the carbon fiber dividers between each crystal

Screenshot of thermal analysis done using 36x30 grid of PbWO4 crystals; maximum temperature: 13.48°C

### 3. Databasing

#### Aaron Brown, Pablo Campero, George Jacobs

- 1. A local DSG MySQL database will be developed for drawings, notes, talks, etc. from each project

- 2. A DSG website search page will be developed as well

#### 4. HV supply cable testing

Peter Bonneau, Aaron Brown, Brian Eng, George Jacobs, Mindy Leffel, and Marc McMullen

- 1. Testing of cable #40, with Radiall connector on one end and flying leads on the other

- Need banana plugs

- Brian Eng will write a testing procedure